作为求职者,应如何看待这个职位

这个职位是做什么的?

职业角色

ASIC Design Engineer是芯片研发体系中的核心技术角色,负责将算法或功能需求转化为可制造的物理电路,其价值在于通过RTL设计、验证与物理实现,确保芯片在性能、功耗、面积(PPA)上达成目标,支撑产品竞争力与量产成功。典型协作对象包括算法工程师、验证工程师、后端物理设计团队及Foundry工艺工程师;关键业务场景集中在芯片架构定义、流片(tape-out)决策与硅后调试;成果导向以时序收敛达标、功耗优化百分比、一次流片成功率为衡量标准。

主要职责

- 根据架构文档完成IP模块或子系统的RTL编码与仿真验证

- 搭建并维护UVM验证环境,执行功能覆盖率与代码覆盖率达标测试

- 协同物理设计团队完成综合、时序分析与功耗完整性(PI)签核

- 主导或参与跨时钟域(CDC)检查、形式验证(Formality)等质量保障流程

- 处理硅后(post-silicon)调试中的逻辑缺陷与性能瓶颈定位

- 编写设计文档、验证计划及流片(tape-out)所需的技术交付物

- 持续优化设计方法与脚本工具,提升团队开发效率与代码质量

行业覆盖

该岗位在消费电子、汽车电子、通信设备、人工智能等领域均有需求,其可迁移能力基础包括数字电路设计、验证方法学、EDA工具链使用。在消费电子行业侧重快速迭代与成本控制,决策周期短,PPA权衡偏向性能与面积;在汽车电子则强调功能安全(ISO 26262)与可靠性,验证流程更严格,协作对象扩展至安全认证机构;在AI芯片领域需深度融合算法与硬件,侧重内存带宽优化与能效比提升。

💡 当前市场对掌握先进工艺节点(7nm及以下)与跨域协同(算法-硬件-软件)能力的设计者需求显著上升,低功耗与可靠性设计成为高价值方向。

AI时代,ASIC Design Engineer会被取代吗?

哪些工作正在被AI改变

在ASIC设计领域,AI正在重塑底层工作方式,通过自动化工具替代部分标准化、重复性任务,主要影响初级工程师的机械执行环节。例如,AI驱动的EDA工具可自动完成代码生成、验证用例生成、时序优化等流程,减少人工干预,但对复杂架构决策、跨域协同和硅后调试等非结构化问题替代有限。

- RTL代码自动生成与优化:AI工具(如Cadence Cerebrus)可根据高层描述自动生成Verilog代码,替代部分手动编码工作,影响初级工程师的模块级设计任务。

- 验证用例智能生成:基于机器学习的验证工具自动生成测试向量,覆盖复杂场景,减少验证工程师的手动用例编写工作量。

- 时序收敛自动化:AI辅助时序分析工具预测关键路径并自动调整约束,替代传统人工迭代优化,加速综合与布局布线流程。

- 设计规则检查(DRC)自动化:AI模型自动识别物理设计违例并提供修复建议,降低后端工程师的手动检查负担。

- 文档自动生成:从设计代码中提取信息自动生成技术文档,减少文档编写中的重复性内容整理工作。

哪些工作是新的机遇

AI加速环境下,ASIC设计岗位正涌现新价值空间,如智能协同设计、算法-硬件融合优化、AI芯片架构创新等。人类工程师角色向系统级策略制定、模型调优与跨域整合演进,AI成为提升设计效率与探索新架构的杠杆,催生如AI-EDA协同专家、智能架构师等新职能。

- 智能架构探索与优化:利用AI模型(如强化学习)自动搜索最优芯片架构方案,工程师负责定义目标函数与验证结果,开拓高性能低功耗设计新路径。

- 算法-硬件协同设计:工程师主导将AI算法(如神经网络)高效映射到定制硬件,优化内存访问、并行计算等,提升AI芯片能效比,创造新商业价值。

- AI辅助硅后调试:结合机器学习分析芯片测试数据,快速定位故障模式,工程师聚焦复杂根因分析与解决方案设计,缩短产品上市时间。

- 自适应EDA工作流设计:工程师设计并管理AI增强的设计流程,整合多工具链,实现动态资源分配与任务调度,提升团队整体产出效率。

- 智能IP集成与验证:利用AI自动化IP选型、接口兼容性检查与集成验证,工程师负责策略制定与质量把关,加速SoC开发周期。

必须掌握提升的新技能

AI时代下,ASIC Design Engineer需强化人机协作能力,新增技能聚焦AI工具应用、模型交互与高阶判断。核心在于掌握AI辅助设计工作流,将AI输出转化为可靠设计决策,并具备跨领域知识整合以应对复杂系统挑战。

- AI-EDA工具链熟练度:掌握主流AI增强EDA工具(如Synopsys DSO.ai、Cadence Cerebrus)的操作与定制,能设计自动化工作流并验证结果准确性。

- Prompt工程与模型交互:具备与AI模型有效交互的能力,如编写精准提示词生成RTL代码或验证计划,并能审校、调试与优化模型输出。

- 数据驱动设计决策:运用机器学习分析设计数据(如功耗、时序报告),识别模式并制定优化策略,将AI洞察转化为具体设计行动。

- 跨域系统整合能力:融合芯片设计、算法原理与软件栈知识,主导AI芯片的端到端开发,确保硬件高效支持AI应用场景。

- 伦理与可靠性审校:在AI辅助设计中承担最终质量把关,评估AI生成设计的可靠性、安全性(如功能安全合规)与伦理影响,确保流片成功。

💡 区分点:自动化工具替代的是标准化执行任务,而人类必须承担架构创新、跨域协同与复杂问题判断等高价值职责。

如何解读行业前景与市场需求?

市场需求总体态势

- 需求覆盖哪些行业: ASIC Design Engineer需求覆盖半导体、通信、消费电子等多个领域,尤其在计算密集型和高能效场景中不可或缺。

- 机会集中在哪些行业: 人工智能、数据中心、自动驾驶等新兴应用推动专用芯片需求,工艺迭代与系统集成复杂度提升持续创造岗位。

- 岗位稳定性分析: 岗位处于芯片研发核心环节,技术壁垒高,受宏观经济波动影响相对较小,长期需求稳定。

热门行业发展

| 热门 Top4 | 核心业务场景 | 技术侧重要求 | 发展特点 |

|---|---|---|---|

| 消费电子 | 智能手机、可穿戴设备芯片设计 | 低功耗、高集成度、快速迭代 | 产品周期短,成本敏感,市场导向 |

| 数据中心与云计算 | AI加速卡、服务器专用芯片 | 高性能计算、能效比、大规模并行 | 技术驱动,高研发投入,生态构建关键 |

| 汽车电子 | 自动驾驶芯片、车载信息娱乐系统 | 高可靠性、功能安全、车规级认证 | 长验证周期,供应链要求严格,安全至上 |

| 通信设备 | 5G基站芯片、网络处理器 | 高速接口、信号处理、协议兼容 | 标准驱动,性能与稳定性并重,迭代较慢 |

💡 匹配个人技术偏好与行业业务节奏,关注验证周期与产品生命周期。

我适合做ASIC Design Engineer吗?

什么样的人更适合这个岗位

适合ASIC Design Engineer的人通常具备系统性思维与细节专注力,能从算法需求推导出电路实现,并在高压流片周期中保持韧性。其价值体系偏向技术深度与问题解决,能量来源于攻克时序收敛、功耗优化等具体挑战,而非快速产出或社交互动,这种特质在芯片行业的长周期、高精度协作生态中能形成稳定优势。

- 偏好从抽象架构到具体电路的系统性拆解,如将神经网络层映射为硬件模块并优化数据流。

- 能在重复仿真与调试中保持耐心,通过波形分析逐层定位深层次bug,而非寻求快速捷径。

- 习惯在PPA(性能、功耗、面积)三角约束中做权衡决策,接受有限资源下的最优解而非完美方案。

- 倾向于独立钻研技术细节(如时钟树综合算法),同时能在跨团队会议中清晰传递设计逻辑与风险。

- 从解决一次流片失败或硅后故障中获得成就感,视技术挑战为成长动力而非压力源。

哪些人可能不太适合

不适合该岗位的常见错位源于工作节奏、信息处理与协作逻辑的不匹配:芯片设计周期长(通常12-24个月)、反馈延迟高,且需在严格约束下处理海量细节。不适应者往往在高压调试中易焦虑,或难以在跨部门博弈中平衡技术理想与现实妥协。

- 期望快速看到成果反馈,难以忍受长达数月的仿真验证与流片等待期。

- 偏好灵活创意发挥,对严格的编码规范、时序约束与设计规则感到束缚。

- 在跨团队协作中倾向于回避技术冲突(如与后端工程师争论时序余量分配)。

- 处理信息时偏好宏观概览,对深入分析日志文件、波形数据等细节缺乏耐心。

- 在资源限制下(如面积预算紧张)容易产生挫败感,而非主动寻找替代方案。

💡 优先评估自身是否能在长周期、高精度、强约束的工作模式下持续成长,而非仅凭短期兴趣判断适配度。

企业文化匹配测试

帮你找到最适合的企业类型和目标公司

如何入行

入行ASIC Design Engineer的核心门槛是掌握数字电路设计全流程能力,可通过EDA工具链使用、RTL代码质量、验证覆盖率与流片项目经验验证。

- 硬件描述语言与设计方法:Verilog/SystemVerilog语法、RTL编码规范、同步/异步电路设计、低功耗设计(UPF)

- 验证方法与工具:UVM验证框架、功能/代码覆盖率、形式验证(Formality)、跨时钟域检查(CDC)

- EDA工具链:仿真工具(VCS/QuestaSim)、综合工具(Design Compiler)、时序分析(PrimeTime)、物理验证(Calibre)

- 芯片实现流程:综合与优化、布局布线(P&R)、时序收敛签核、功耗完整性分析

- 项目交付物:设计规格文档、验证计划与报告、网表(netlist)文件、流片(tape-out)数据包

- 行业标准与协议:AMBA总线协议(AXI/AHB)、DDR/JESD接口标准、汽车功能安全(ISO 26262)、芯片测试(DFT/ATPG)

需从零构建数字电路知识体系,最小能力闭环包括硬件描述语言、基础工具使用与可验证的小型项目产出。

- 通过在线课程(如Coursera VLSI专项)掌握Verilog与UVM基础

- 使用EDA云平台(如Efabless)完成简单IP模块设计

- 产出个人作品集:如UART/SPI控制器RTL代码与仿真报告

- 参与开源社区(如RISC-V)的硬件贡献,积累协作经验

- 完成一次从RTL到GDSII的完整流程学习(可通过教学项目)

更匹配微电子、集成电路、电子工程等专业背景,需重点补齐EDA工具实战经验与项目全流程理解,避免仅停留在理论课程。

- 参与学校/实验室的FPGA或ASIC流片项目

- 完成Verilog数字电路课程设计(如CPU/通信模块)

- 学习并使用UVM搭建验证环境

- 掌握至少一种EDA工具(如Vivado/Quartus)的完整流程

- 产出可展示的RTL代码、仿真波形与覆盖率报告

可从FPGA开发、嵌入式硬件、验证工程师等岗位迁移,优势在于硬件基础与工具熟悉度,需补齐ASIC特定流程(如物理设计、流片)与行业协议深度。

- 将FPGA项目经验转化为ASIC设计案例(关注时序、面积优化)

- 从验证岗位延伸至RTL设计,掌握综合与时序分析

- 学习先进工艺节点设计规则与物理效应

- 参与开源ASIC项目(如OpenTitan)积累流片流程经验

- 考取行业认证(如Cadence/Synopsys工具认证)提升可信度

💡 优先积累流片项目经验与可验证的PPA数据,公司光环或起点标签在芯片行业远不如实际设计能力重要。

作为求职者,如何分析这个职位的成长

有哪些职业成长路径?

专业深化路径

ASIC Design Engineer的专业成长围绕芯片设计全流程深化,需突破从模块级到系统级的架构瓶颈,掌握从RTL到GDSII的完整实现能力,典型瓶颈包括时序收敛、功耗优化和DFT插入等后端挑战。

- 初级工程师阶段:负责IP模块RTL编码与验证,需通过公司内部代码评审和覆盖率达标考核,掌握UVM验证方法学。

- 中级工程师阶段:主导子系统集成与综合,需解决跨时钟域同步问题,通过时序签核(sign-off)考核,熟悉UPF低功耗设计流程。

- 高级工程师阶段:负责芯片顶层架构与物理实现,需主导floorplan规划与功耗完整性分析,掌握先进工艺节点(如7nm以下)的物理设计规则。

- 专家/架构师阶段:定义芯片微架构与性能指标,需主导芯片tape-out前的最终验证(final sign-off),具备解决先进封装(如Chiplet)集成问题的能力。

适合对数字电路底层原理有极致追求、能承受流片(tape-out)前高压调试、擅长在PPA(性能、功耗、面积)三角约束中寻找最优解的技术钻研者。

团队与组织路径

向管理发展需从技术Lead转型,典型路径为设计经理→技术总监,核心是协调前端设计、后端实现与验证团队的资源博弈,管理流片周期与多项目并行风险。

- 技术主管(Tech Lead):负责3-5人设计小组,主导模块间接口协议制定,需协调验证团队完成跨模块验证(cross-module verification)。

- 设计经理:管理10人以上设计团队,负责芯片项目进度与资源分配,需主导与Foundry的工艺对接和MPW(多项目晶圆)流片决策。

- 技术总监:统筹前端设计、后端物理与DFT团队,制定芯片技术路线图,需处理跨部门(如与算法、软件团队)的架构对齐会议。

- 研发总监/VP:负责产品线技术战略,管理预算与IP采购(如第三方IP集成),主导芯片量产前的良率提升与故障分析(FA)。

适合擅长在硅前(pre-silicon)与硅后(post-silicon)团队间搭建协作桥梁、能应对流片延期风险、精通芯片设计全流程资源调配的沟通协调者。

跨领域拓展路径

横向拓展聚焦芯片与系统、算法的融合,常见方向包括向FPGA原型验证、芯片架构算法协同设计转型,或切入汽车电子、AI加速器等新兴领域。

- 向芯片验证专家转型:深入FPGA原型验证或硬件仿真(emulation),需掌握SystemVerilog断言与形式验证工具,服务汽车功能安全(ISO 26262)认证。

- 向系统应用工程师(SAE)转型:负责芯片客户支持,需理解终端应用场景(如摄像头ISP处理),解决芯片在客户板级的调试问题。

- 向算法硬件协同设计转型:参与AI加速器设计,需掌握神经网络量化与硬件映射,熟悉TensorFlow/PyTorch模型到RTL的转换流程。

- 向芯片创业或产品经理转型:主导芯片定义与市场对接,需洞察行业趋势(如Chiplet生态),协调设计团队与Foundry、封装厂资源。

适合对芯片应用场景有强烈好奇心、能快速学习跨领域知识(如算法、软件)、擅长在硬件限制中挖掘系统级优化机会的跨界整合者。

💡 成长年限通常为:初级到高级工程师需3-5年(以独立负责子系统签核为标志),高级到专家需5-8年(以主导完整芯片流片为标志)。管理路线晋升更依赖项目交付与团队规模(如带10人以上团队),专家路线侧重技术深度与专利/论文产出。关键判断标准:能否在流片前解决关键时序违例(timing violation),或能否在资源冲突中平衡多项目优先级。管理路线需强化风险管控与跨部门谈判能力,专家路线需深耕先进工艺节点或特定领域(如高速SerDes)。

如何规划你的职业阶段?

初级阶段(0-3年)

作为ASIC设计新人,你常陷入RTL编码与验证的细节循环,面临时序收敛失败、覆盖率不足等具体困境,同时困惑于该专注数字前端还是涉猎物理设计。成长焦虑源于对芯片流片(tape-out)流程的陌生,以及如何在IP复用与自主设计间找到平衡。我该选择进入头部芯片公司接受标准化流程训练,还是加入初创团队快速接触全流程?

- 大公司/小公司:头部公司(如海思、展锐)提供严格的代码评审与UVM验证体系,但可能局限在特定模块;初创团队让你快速参与从架构到GDSII的全流程,但缺乏成熟流程支撑,易陷入设计反复。

- 专项成长/全面轮岗:专注前端设计需深挖SystemVerilog与功耗优化(UPF),但可能错过物理设计知识;轮岗接触综合、DFT可建立全局观,但初期难以形成技术深度。

- 学习型/实践型:依赖公司培训掌握标准流程(如DC综合、Formality形式验证),但创新受限;主动参与开源项目(如RISC-V核设计)能锻炼问题解决能力,但缺乏工业级验证环境。

中级阶段(3-5年)

此时你已能独立负责子系统设计,但面临从模块到芯片级的跨越瓶颈:如何平衡PPA(性能、功耗、面积)三角约束?常见迷思是继续深耕技术细节,还是转向技术管理协调跨团队冲突。晋升断层往往出现在能否主导一次完整MPW(多项目晶圆)流片,并解决硅后调试中的关键问题。我该聚焦成为时钟树综合专家,还是转型为设计经理管理验证与后端团队?

- 技术路线:深入特定领域如高速SerDes设计,需掌握信道建模与均衡算法,但可能受限于工艺节点演进;或专攻低功耗设计,主导芯片级UPF流程,但需应对多电压域带来的验证复杂度。

- 管理路线:转型技术主管(Tech Lead),负责3-5人小组的模块集成,核心挑战是协调前端设计与验证团队的进度冲突,以及处理与Foundry的工艺文件对接。

- 行业选择:坚守消费电子芯片追求迭代速度,但面临激烈成本竞争;转向汽车电子需掌握功能安全(ISO 26262)与可靠性设计,但认证周期长、门槛高。

高级阶段(5-10年)

你已成为芯片项目的关键决策者,影响力体现在架构定义与流片风险评估上。新门槛是如何在算法需求与硬件限制间找到最优解,以及管理跨部门(软件、算法、封装)的资源博弈。角色转变从技术执行者升级为技术布道者,需在行业会议分享设计经验或主导内部技术培训。我能成为定义下一代AI加速器微架构的关键人物吗?如何平衡技术深度与团队规模扩张带来的管理负荷?

- 专家路线:成为芯片架构师,主导性能建模与功耗分析,影响力体现在专利产出与行业标准参与,但需持续跟踪Chiplet、存算一体等新兴技术趋势。

- 管理者/带教:晋升设计总监,管理20人以上团队,核心职责是制定技术路线图与处理流片危机(如时序违例爆发),同时建立内部带教体系培养新人。

- 行业平台型:加入EDA公司(如Synopsys、Cadence)担任应用工程师,为芯片公司提供工具支持,影响力从单一项目扩展到行业生态,但需适应从设计者到方案支持者的角色转换。

资深阶段(10年以上)

你已见证多个工艺节点演进,面临从技术领导者到行业定义者的再定位。核心问题是如何在技术传承(如培养下一代架构师)与创新突破(如探索量子计算芯片)间找到平衡,以及个人价值从项目成功转向行业生态贡献。社会影响体现在参与行业标准制定、或通过技术投资孵化新兴芯片公司。如何持续焕新影响力?是转型为芯片领域的天使投资人,还是投身高校培养基础研究人才?

- 行业专家/咨询顾问:为芯片创业公司提供架构评审与流片风险评估,按项目收取高额咨询费,但需建立广泛的行业人脉与信誉背书。

- 创业者/投资人:创办专注于细分领域(如RISC-V生态、自动驾驶芯片)的初创公司,或转型VC投资早期芯片项目,核心挑战是判断技术趋势与市场窗口的匹配度。

- 教育者/知识传播者:在高校开设VLSI设计课程,或通过技术社区(如EETOP)传播实践经验,影响力从商业成功扩展到人才培养,但需适应学术与工业界的节奏差异。

💡 行业普遍经验:从初级到独立负责子系统约需3年(以通过时序签核为标志),到主导流片需5-8年(以成功量产为标志)。晋升关键不在年限,而在‘流片履历’——参与过几次MPW、解决过哪些硅后bug。技术路线晋升看专利/论文产出与架构定义能力,管理路线看团队规模与项目交付记录。隐性门槛包括:能否在压力下完成流片前最后一周的‘死亡调试’,以及是否具备与Foundry工程师直接谈判工艺问题的能力。

你的能力发展地图

初级阶段(0-1年)

作为ASIC设计新人,你主要承担IP模块的RTL编码与基础验证任务,需快速掌握公司内部设计流程(如从spec到netlist的标准化步骤)和EDA工具链(VCS/DC/PT)。典型困惑包括时序约束(SDC)编写不当导致综合失败、UVM验证环境搭建缓慢。行业特有节奏是跟随项目MPW(多项目晶圆)周期,在流片(tape-out)前高压调试中学习。如何在该行业6-12个月的入门周期内,建立对代码质量(lint/CDC检查)和验证覆盖率(code/functional)的可信赖执行力?

- 掌握Verilog/SystemVerilog语法与RTL编码规范

- 熟悉UVM验证方法学与testbench搭建流程

- 理解时序约束(SDC)与综合(DC)基础操作

- 学会使用版本管理(Git)与问题追踪(Jira)系统

- 适应跨时钟域(CDC)检查与形式验证(Formality)流程

- 完成模块级仿真与覆盖率达标(95%+)交付

能独立完成一个中等复杂度IP模块(如UART、SPI控制器)的RTL设计、验证环境搭建、综合时序收敛,并通过团队代码评审与覆盖率签核(sign-off),错误率低于千行代码5个bug。

发展阶段(1-3年)

此时你开始负责子系统(如CPU缓存控制、DDR接口)集成,需独立解决跨模块接口协议冲突、功耗域(power domain)划分问题。典型进阶路径是从执行验证用例转向主导验证计划(verification plan),并参与硅后(post-silicon)调试中的逻辑分析仪(LA)抓取。行业问题排查模式依赖波形调试(Verdi)与断言(assertion)定位,协作关键是与后端工程师协商时序余量(timing margin)。我是否具备主导一个汽车电子芯片中安全岛(safety island)模块,并满足ISO 26262 ASIL-B等级验证要求的能力?

- 掌握子系统级UPF低功耗设计与验证流程

- 能独立完成跨时钟域(CDC)与复位域同步方案

- 熟练使用波形调试工具(Verdi)定位深层次bug

- 理解物理设计对时序的影响,参与floorplan讨论

- 主导模块间接口协议(如AMBA AXI)一致性验证

- 建立硅前(pre-silicon)到硅后(post-silicon)的调试链路

能独立承担一个包含3-5个IP模块的子系统设计,完成从RTL到网表(netlist)的完整流程,时序收敛(setup/hold)达标,功耗报告符合预算,并通过子系统级形式验证与门级仿真(gate-level simulation)。

中级阶段(3-5年)

你进入芯片级系统化设计阶段,需主导芯片顶层集成与架构权衡。真实样貌包括构建芯片级验证环境(chip-level UVM)、定义功耗管理单元(PMU)策略,以及协调前端设计、后端实现与封装团队的资源冲突。体系建设点体现在制定公司内部设计检查清单(checklist)、优化综合脚本(tcl)流程。行业复杂场景如处理多电压域(multi-voltage)下的电源门控(power gating)验证,或解决先进工艺(7nm以下)的电磁干扰(EMI)问题。如何从执行者转变为一次完整MPW流片的技术负责人,统筹时钟树综合(CTS)与DFT插入的协同?

- 主导芯片级验证环境搭建与回归测试(regression)策略

- 制定时序收敛(timing closure)与功耗完整性(PI)签核标准

- 优化物理设计流程(从综合到布局布线)的自动化脚本

- 推动设计方法学(如基于IP的SoC集成)在团队内落地

- 建立芯片级调试(debug)方法论,缩短硅后问题定位时间

- 主导与Foundry的工艺文件(PDK)对接与设计规则检查(DRC)

能主导一颗中等规模芯片(如物联网MCU)从架构到GDSII的全流程,定义PPA(性能、功耗、面积)目标并达成,成功流片并实现量产,团队内建立可复用的设计流程与知识库。

高级阶段(5-10年)

你成为芯片技术战略的关键影响者,角色从项目主导升级为技术路线定义。行业战略视角体现在判断工艺节点迁移(如从28nm到14nm)的性价比、评估Chiplet(芯粒)集成的可行性。组织影响通过建立内部技术委员会、制定芯片设计规范(design guideline)实现。特有大型场景如领导一颗AI训练芯片的架构定义,需权衡Tensor核心数量、内存带宽与散热限制。如何影响公司芯片技术选型,推动团队采用开源EDA工具或RISC-V生态,以降低设计成本?

- 定义芯片微架构与性能模型(performance model),指导算法硬件协同设计

- 主导先进技术(如3D-IC、存算一体)的预研与风险评估

- 建立跨部门(硬件、软件、算法)的技术对齐与决策机制

- 推动行业标准参与(如UCIe接口协议)或专利布局

- 构建芯片设计人才培养体系与知识传承(如内部培训、技术评审)

持续影响力体现在主导公司核心芯片产品线技术路线图,推动一次重大技术变革(如从ARM转向RISC-V架构),或通过行业演讲、专利授权形成外部技术品牌,团队设计效率提升30%以上。

💡 芯片设计能力价值最终由流片成功次数与量产规模定义,市场更青睐能平衡创新与风险、在先进工艺节点有实战经验的架构决策者。

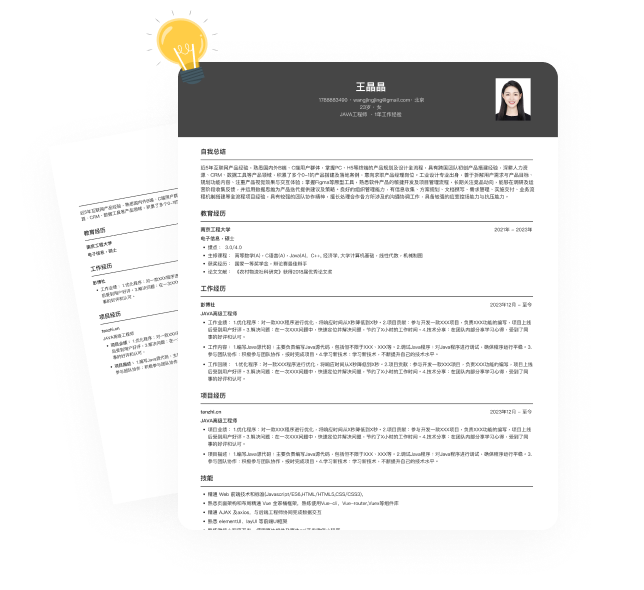

作为求职者,如何构建匹配职位能力的简历

不同阶段,应突出哪些核心能力?

ASIC Design Engineer的价值评估是一个动态过程,随经验增长,怎么写简历才不会显得要么太浅,要么过度包装?

- 能力侧重:能完成IP模块的RTL编码与基础验证,掌握Verilog/SystemVerilog语法和UVM验证环境搭建,通过代码评审和覆盖率达标考核,适应公司内部设计流程和EDA工具链。

- 表现方式:使用“完成”“实现”“协助”等动词,结合模块功能、验证覆盖率、代码质量等可量化指标,描述在导师指导下完成的具体任务。

- 示例描述:完成UART控制器IP模块的RTL编码与验证,实现功能覆盖率100%,代码通过lint/CDC检查零错误。

- 能力侧重:能独立负责子系统(如DDR接口、缓存控制)设计,解决跨模块接口协议和时序收敛问题,主导验证计划并参与硅后调试,掌握功耗分析和物理设计协同。

- 表现方式:使用“负责”“主导”“解决”等动词,结合子系统规模、时序余量、功耗优化百分比等结果,展示独立承担模块级任务的能力。

- 示例描述:负责SoC中DDR4 PHY子系统设计,时序收敛达标,功耗较上一代降低15%,成功流片并量产。

- 能力侧重:能主导芯片级集成与架构权衡,制定验证策略和时序签核标准,优化物理设计流程,协调前端、后端与封装团队,具备MPW流片技术负责经验。

- 表现方式:使用“主导”“制定”“优化”等动词,结合芯片规模、流片成功率、流程效率提升等指标,体现系统级设计和管理能力。

- 示例描述:主导一颗物联网MCU芯片从架构到GDSII全流程,成功流片并量产,团队设计效率提升25%。

- 能力侧重:能定义芯片技术路线图和微架构,评估先进工艺与封装方案,推动跨部门技术对齐与行业标准参与,建立设计规范和人才培养体系,影响产品战略。

- 表现方式:使用“定义”“推动”“建立”等动词,结合技术变革成果、专利数量、团队效能提升等战略级贡献,展示行业影响力。

- 示例描述:定义公司AI加速芯片技术路线,推动采用RISC-V架构,相关专利授权5项,产品线成本降低20%。

💡 芯片设计简历看流片履历、模块复杂度与PPA达成数据,资深岗位需突出架构定义与行业生态贡献。

如何呈现你的工作成果?

从“能做事”到“能成事”的演化路径,随着经验增长,成果的呈现重点会不断上移,从技术执行到业务成效,再到组织与战略影响

- 成果侧重点:模块级设计或验证任务的交付物,如通过签核的RTL代码、达到覆盖率目标的验证环境、零错误的lint/CDC检查报告,以及被项目采纳的IP模块。

- 成果呈现方式:交付物名称 + 质量/覆盖率指标 + 采纳状态。例如:UART控制器IP模块,功能覆盖率100%,被2个SoC项目复用。

- 示例成果句:SPI控制器IP模块RTL代码通过形式验证,lint检查零错误,被项目组采纳并集成。

- 成果侧重点:子系统(如接口、存储控制)的完整实现与流片结果,包括时序收敛达标、功耗优化百分比、硅后调试问题解决数量,以及量产芯片中的稳定运行。

- 成果呈现方式:子系统名称 + PPA(性能、功耗、面积)优化指标 + 流片/量产结果。例如:DDR4 PHY子系统,功耗降低18%,随主芯片成功流片并量产100K颗。

- 示例成果句:负责的Cache子系统时序收敛余量提升10%,随物联网芯片流片成功,硅后零功能缺陷。

- 成果侧重点:完整芯片从设计到量产的端到端成果,包括流片成功率、设计周期缩短比例、团队流程效率提升,以及芯片在终端产品的市场表现(如出货量、成本降低)。

- 成果呈现方式:芯片产品/项目名称 + 关键结果指标(流片成功、效率、成本) + 市场/团队影响范围。例如:主导的蓝牙音频芯片,一次流片成功,设计周期缩短30%,成本降低15%。

- 示例成果句:某智能手表主控芯片一次流片成功,量产500万颗,团队综合脚本使物理设计效率提升25%。

- 成果侧重点:技术路线变革成果(如架构迁移、工艺升级)、行业标准贡献(专利、论文)、设计体系效能提升(团队产出翻倍、错误率下降),以及产品线战略影响(市场份额增长、生态建立)。

- 成果呈现方式:战略举措/技术方向 + 量化业务影响 + 行业/组织范围。例如:推动公司转向RISC-V架构,相关产品线成本降低22%,获得3项核心专利授权。

- 示例成果句:定义并落地的AI推理芯片架构,使产品能效比提升2倍,助力公司在该细分市场占有率从15%增至30%。

💡 成果从‘模块交付’升级为‘流片成功’,再进阶到‘技术路线影响’与‘市场结果’,每个阶段都需用可验证的行业硬指标说话。

还没准备好简历?

谈职专业简历编辑器,10分钟搞定!

HR是如何筛选简历的?

HR初筛ASIC Design Engineer简历时,通常在15-30秒内扫描关键词(如RTL、UVM、时序收敛、流片)、项目规模(芯片类型、工艺节点)、成果指标(PPA数据、覆盖率、流片次数)。优先查看工作经历中的芯片产品名称、负责模块复杂度、EDA工具链,以及教育背景中的微电子/集成电路专业。简历结构偏好倒序排列,关键信息落点在项目描述的具体技术动作与量化结果上。

真实性验证

HR通过可追溯的记录交叉核验简历真实性,关注项目周期、角色权重、交付物的可查性,以及成果与行业公开数据的逻辑一致性。

- 项目可追溯性验证:通过LinkedIn项目更新、GitHub代码仓库(如有开源贡献)、专利数据库查询来核验技术参与度。

- 角色与贡献位置核查:对照项目时间线、团队规模,判断候选人所声称的‘主导’或‘负责’是否合理,例如流片周期通常为6-18个月。

- 成果状态确认:如量产芯片名称可在公司官网或行业报告中查到,专利号可公开检索,论文可被学术数据库收录。

公司文化适配

HR从简历文本风格、成果结构、职业轨迹中推断文化适配度,基于可观察线索判断候选人的风险偏好、节奏耐受和协作倾向。

- 表述方式映射工作模式:如偏重‘优化时序’、‘降低功耗’体现执行与优化导向,适合成熟团队;‘探索Chiplet集成’、‘定义新架构’体现创新导向,适合研发型团队。

- 成果结构反映价值取向:强调‘流片成功率’、‘量产规模’偏向结果驱动文化;突出‘方法学创新’、‘流程效率提升’偏向过程优化文化。

- 职业轨迹显示稳定性偏好:长期深耕单一领域(如始终做处理器设计)匹配稳健组织;频繁切换赛道(如从消费电子转到汽车电子)适配快速迭代环境。

核心能力匹配

HR聚焦能力验证信号,通过简历中描述的具体技术动作、工具使用、成果指标来评估能力深度,优先匹配岗位JD中的关键词和任务类型。

- 关键技术栈与工具熟练度:是否明确列出Verilog/SystemVerilog、UVM、DC/PT、Verdi等,并展示在项目中的应用场景。

- 可量化成果呈现:如时序收敛余量(slack)、功耗降低百分比、验证覆盖率、流片成功次数、芯片出货量等硬指标。

- 行业流程理解:是否体现从RTL到GDSII的全流程参与,或特定环节(如综合、DFT、物理验证)的专精经验。

- 与JD关键词一一对应:简历描述需直接使用岗位要求中的术语,如‘时序签核’、‘功耗完整性分析’、‘跨时钟域检查’。

职业身份匹配

HR通过职位头衔(如设计工程师、高级工程师、架构师)与项目职责的对应关系判断身份匹配度,重点考察候选人参与项目的芯片类型(如消费电子、汽车电子)、工艺节点(如28nm、7nm)、以及模块/子系统/芯片级的责任范围。

- 职位等级与职责是否匹配:例如‘高级工程师’应主导子系统或参与芯片级设计,而非仅完成IP模块编码。

- 项目赛道与深度是否清晰:如汽车电子芯片需体现功能安全(ISO 26262)经验,AI芯片需展示神经网络加速器设计参与度。

- 技术栈与岗位同轨:简历中需出现岗位JD指定的关键技术,如SystemVerilog、UPF低功耗设计、AMBA总线协议。

- 行业资历标签有效性:如‘成功流片’次数、‘量产芯片’名称、‘专利/论文’数量,这些是硬性身份信号。

💡 HR初筛优先扫描关键词匹配与成果硬指标,身份断层、能力描述空洞或成果不可验证会直接否决,文化适配在技术过关后作为差异化判断。

如何让你的简历脱颖而出?

了解 HR 的关注点后,你可以主动运用以下策略来构建一份极具针对性的简历。

明确职业身份

在简历开头用3秒建立ASIC Design Engineer身份:采用行业标准头衔(如“高级ASIC Design Engineer”),明确主攻方向(如“数字前端设计/低功耗架构”),标注细分领域(如“汽车电子芯片/AI加速器”)。避免泛化描述,直接使用“RTL设计”“时序收敛”“流片”等强关联词。

- 采用“岗位级别+专业方向+领域标签”结构,如“资深ASIC Design Engineer(数字前端,专注汽车功能安全芯片)”。

- 在摘要中嵌入关键术语:如“掌握UVM验证方法学”“精通UPF低功耗设计”“具备7nm以下工艺流片经验”。

- 使用行业公认身份标签:如“芯片架构师候选人”“子系统设计负责人”“硅后调试专家”。

- 关联具体产品类型:如“智能手机AP芯片”“物联网MCU”“自动驾驶域控制器”。

示例表达:资深ASIC Design Engineer,专注数字前端设计与低功耗架构,在汽车电子芯片领域具备从RTL到GDSII的全流程经验,主导过多次成功流片。

针对不同岗位调整策略

根据目标岗位方向调整简历重心:技术专家岗突出深度技术成果与专利;管理岗强调团队规模、项目交付与流程建设;跨界岗(如芯片产品经理)侧重市场洞察、需求转化与生态合作。表达从工具细节转向业务影响。

- 技术专家路线:成果口径聚焦PPA极致优化、先进工艺突破、专利/论文产出;技能排列优先EDA工具深度、架构建模能力;案例选择突出高复杂度模块或芯片级技术攻关。

- 管理/团队领导路线:成果口径转向流片成功率、团队效率提升、人才培养数量;技能排列强调跨部门协调、资源分配、风险管控;案例选择展示多项目并行管理或危机处理(如流片延期补救)。

- 跨界/产品路线:成果口径关注芯片定义准确性、上市时间、市场份额;技能排列侧重需求分析、竞品对标、供应链协调;案例选择体现从市场调研到芯片量产的完整闭环。

示例表达:(技术专家示例)提出新型时钟门控方案,获中美专利授权,应用于公司多款芯片,平均动态功耗降低18%。

展示行业适配与个人特色

通过行业专属场景和难点解决方案展现不可替代性:描述处理先进工艺节点(如5nm)的物理效应、解决汽车芯片功能安全认证、或优化AI芯片内存带宽瓶颈等具体挑战。突出在跨团队协作(如与算法、软件、封装团队对接)中的关键角色。

- 先进工艺经验:如“处理7nm工艺下IR-drop与电磁干扰问题,确保芯片电源完整性达标”。

- 功能安全实践:如“主导ISO 26262 ASIL-B等级芯片的DFT插入与故障注入测试,通过第三方认证”。

- 跨域协同能力:如“协调算法团队量化神经网络模型,设计专用硬件加速器,使推理速度提升5倍”。

- 硅后调试专长:如“通过逻辑分析仪抓取与波形分析,定位并修复量产芯片中深层次时钟域同步bug”。

- 方法学创新:如“引入形式验证替代部分动态仿真,将验证周期缩短40%,错误检出率提升至100%”。

- 生态参与:如“参与RISC-V开源社区,贡献处理器核优化代码,被3个商用项目采纳”。

示例表达:在5nm AI训练芯片项目中,解决HBM2E接口时序闭合难题,使内存带宽利用率达90%,芯片算力较竞品提升15%。

用业务成果替代表层技能

将技能描述转化为可验证的业务成果:用PPA(性能、功耗、面积)优化数据、流片成功率、量产规模、设计周期缩短等硬指标替代“熟悉XX工具”。成果表达需体现对芯片成本、上市时间、可靠性的实际影响。

- 时序收敛成果:如“将关键路径时序余量从-50ps优化至+100ps,确保芯片一次流片成功”。

- 功耗优化成果:如“通过UPF流程优化,使待机功耗降低40%,延长终端设备电池寿命20%”。

- 验证效率成果:如“重构UVM验证环境,将回归测试时间从48小时缩短至12小时,覆盖率提升至99.5%”。

- 流片与量产成果:如“主导的蓝牙音频芯片一次流片成功,量产超500万颗,客户退货率低于0.01%”。

- 流程改进成果:如“开发自动化综合脚本,使物理设计周期缩短30%,团队人力投入减少2人/月”。

- 成本控制成果:如“通过架构优化将芯片面积缩小15%,单颗成本降低12%,年节省晶圆费用约200万美元”。

示例表达:优化DDR子系统功耗管理单元,使动态功耗降低25%,随主芯片流片成功并量产1000万颗,客户功耗测试达标率100%。

💡 差异化核心在于用行业硬指标证明价值,优先展示流片履历、PPA数据和量产影响,而非技能列表。

加分亮点让你脱颖而出

这些是简历中能让你脱颖而出的'加分项':在ASIC设计领域,HR在初筛时特别关注超越常规技能要求的差异化特质,如先进工艺实战经验、行业标准参与、跨域协同能力等。这些亮点能直接证明你的专业深度、创新潜力与行业影响力,显著提升岗位匹配度。

先进工艺节点流片实战经验

在芯片行业,掌握7nm及以下先进工艺节点的设计、验证与流片能力是稀缺资源。HR关注此项是因为它直接关联芯片性能、成本竞争力与技术前瞻性,涉及处理FinFET物理效应、多 patterning、IR-drop分析等复杂挑战,能证明候选人具备应对未来技术迭代的硬实力。

- 主导或深度参与5nm/3nm工艺芯片的时序收敛与物理验证,解决过先进节点特有的电磁干扰(EMI)问题。

- 优化过先进工艺下的功耗完整性(PI)方案,如使用自适应电压调节(AVS)技术降低动态功耗。

- 处理过极紫外光刻(EUV)相关的设计规则检查(DRC)违例,确保制造良率。

- 参与过与Foundry的工艺文件(PDK)联合调试,缩短了设计到流片的周期。

示例表达:在5nm AI训练芯片项目中,解决HBM3接口时序闭合难题,使芯片一次流片成功,性能较上一代提升40%。

功能安全与可靠性设计认证

随着汽车电子、工业控制等领域的芯片需求增长,功能安全(如ISO 26262)与可靠性设计成为关键门槛。HR重视此项是因为它涉及严格的流程认证、故障注入测试、安全机制设计,能证明候选人具备高可靠性芯片的开发能力,适配车规级、工规级等高价值市场。

- 主导过ISO 26262 ASIL-B/C/D等级芯片的完整开发流程,包括安全需求定义、硬件架构度量(FMEDA)与验证。

- 设计并验证过安全机制,如ECC内存保护、锁步核(lockstep core)、看门狗定时器,并通过故障注入测试。

- 参与过第三方功能安全审计(如TÜV认证),并推动团队流程改进以符合标准要求。

- 在芯片中实现过AEC-Q100可靠性测试要求,如HTOL(高温工作寿命)与ESD防护设计。

示例表达:负责汽车MCU芯片的功能安全设计,通过ISO 26262 ASIL-B认证,安全机制覆盖率达99%,客户零安全事故报告。

芯片架构创新与专利产出

在竞争激烈的芯片市场,架构级创新(如存算一体、Chiplet集成)能带来性能突破或成本优势。HR关注此项是因为它体现候选人的技术领导力与行业贡献,专利、论文或开源项目成果是硬性证据,能提升公司在知识产权与生态构建中的竞争力。

- 主导过新型芯片架构定义,如基于RISC-V的定制化处理器、存内计算(PIM)加速器,并实现性能指标突破。

- 拥有授权发明专利(如中美欧专利),内容涉及低功耗电路、高速接口或验证方法学创新。

- 在行业顶级会议(如ISSCC、DAC)发表过论文,或为开源项目(如OpenTitan、RISC-V核)贡献核心代码。

- 推动过公司内部设计方法学变革,如引入敏捷芯片设计流程,缩短产品迭代周期。

示例表达:提出并实现一种可配置的神经网络加速器架构,获3项中美专利授权,使芯片能效比提升2倍,被用于边缘AI产品线。

全流程协同与硅后调试专长

芯片设计涉及前端、后端、验证、封装等多团队协作,硅后调试能力直接决定量产效率。HR看重此项是因为它证明候选人具备系统级视角与问题解决韧性,能处理从设计缺陷到量产故障的复杂链路,减少项目风险与成本超支。

- 主导过从架构定义到GDSII交付的全流程协调,解决过前端设计与物理实现的时序冲突。

- 在硅后调试中,使用逻辑分析仪(LA)或片上调试(OCD)工具定位并修复过深层次功能或性能问题。

- 优化过芯片测试(ATE)向量,将量产测试时间缩短20%以上,提升工厂吞吐量。

- 协调过与封装厂(OSAT)的联合分析,解决过芯片封装引起的信号完整性问题。

示例表达:在量产芯片调试中,快速定位并修复DDR PHY时钟抖动问题,使良率从85%提升至99%,节省潜在损失超100万美元。

💡 亮点需用行业硬证据支撑(如专利号、认证名称、具体指标),避免主观描述,让HR通过可验证成果判断你的真实价值。

市场偏爱的深层特质

以下这些特质,是市场在筛选该类岗位时格外关注的信号:在ASIC设计领域,随着技术迭代加速和行业竞争加剧,企业不仅看重技术硬实力,更关注候选人的长期潜力与组织价值。这些深层特质反映了应对复杂挑战、驱动创新和适应未来的能力,是评估人才稀缺性的关键依据。

技术前瞻与趋势洞察

在芯片行业,技术迭代周期短(如每2-3年工艺节点演进),市场偏爱能提前布局新兴技术(如Chiplet、存算一体、RISC-V生态)的候选人。该特质体现为对行业趋势的敏感度,能预判技术拐点并推动团队提前储备,降低公司长期研发风险,是架构师和高级技术领导的核心潜力信号。

- 在项目中主动引入或评估新兴技术方案,如参与Chiplet原型验证或开源RISC-V核优化。

- 通过行业会议、专利分析或技术预研报告,推动团队调整技术路线图以应对市场变化。

- 在简历中展示对先进工艺节点(如3nm)或新兴架构(如量子计算芯片)的持续跟踪与学习成果。

跨域系统整合能力

现代芯片设计日益复杂,需协同算法、软件、封装、测试等多领域。市场看重候选人能打破技术孤岛,在系统层面优化PPA(性能、功耗、面积)与成本。该特质体现为从单一模块设计者升级为系统级问题解决者,能协调跨团队资源,应对汽车电子、AI芯片等融合场景的集成挑战。

- 主导或深度参与芯片级集成项目,解决过算法硬件协同设计、封装信号完整性或硅后软硬件联调问题。

- 在协作中主动建立跨部门沟通机制(如定期技术对齐会),缩短决策周期并减少设计反复。

- 成果描述中体现对终端应用场景(如自动驾驶时延要求、AI模型精度损失)的理解与硬件优化对应。

风险预判与韧性调试

芯片流片成本高昂(一次可达数百万美元),市场偏爱能在设计早期识别风险(如时序违例、功耗热点)、并在硅后高压调试中展现韧性的候选人。该特质体现为对设计全流程的深度掌控与问题解决耐力,能通过方法论(如形式验证、故障注入)降低流片失败概率,是保证项目成功的关键稀缺能力。

- 在项目中提前引入风险评估(如使用静态时序分析工具预警关键路径),并推动团队制定应对预案。

- 有硅后调试成功案例,如使用逻辑分析仪定位深层次bug,并在时间压力下完成修复与验证。

- 建立或优化过团队内部的设计检查清单(checklist)或调试流程,减少重复性错误发生频率。

工程方法学创新驱动

随着芯片规模增大,传统设计方法面临效率瓶颈。市场关注能推动工程方法学变革(如敏捷芯片设计、AI辅助EDA工具应用)的候选人。该特质体现为不满足于现有流程,能通过自动化脚本、工具链优化或新验证方法提升团队产出效率,是组织效能提升的长期价值贡献者。

- 开发过自动化脚本(如Tcl/Python)优化综合、布局布线或验证流程,显著缩短设计周期。

- 主导过方法学试点项目,如引入UVM寄存器模型自动生成或基于云平台的协同设计环境。

- 在成果中展示流程改进的具体影响,如团队人均产出提升、项目交付时间缩短或错误率下降数据。

💡 这些特质应自然融入项目描述,通过具体行动和成果证据(如“主导Chiplet预研缩短产品上市时间”)展现,而非单独罗列抽象词汇。

必须规避的表述陷阱

本部分旨在帮助你识别简历中易被忽视的表达陷阱:在ASIC设计领域,简历的专业度与可信度直接影响HR筛选结果。常见误区包括技术描述模糊、成果逻辑断裂、角色夸大等,这些陷阱会削弱简历说服力,甚至引发真实性质疑。通过规避这些陷阱,可确保内容真实、条理清晰且高度匹配岗位需求。

技术术语堆砌无上下文

在简历中罗列大量技术术语(如UVM、UPF、CDC),但缺乏具体应用场景或成果关联,HR难以判断真实掌握深度。这常见于初级或转行候选人,易被视为‘关键词填充’而非能力证明,削弱简历的专业可信度,尤其在芯片设计这种强调实践验证的行业。

- 为每个技术术语附加简短应用示例,如‘使用UVM搭建AXI总线验证环境,覆盖率达标99%’。

- 将术语嵌入项目描述,说明其在解决具体问题(如时序收敛、功耗优化)中的作用与结果。

- 避免孤立列出工具名称,改为‘熟练使用Verdi进行波形调试,平均定位bug时间缩短50%’。

成果描述缺乏因果链

仅陈述结果(如‘功耗降低20%’)而未说明行动与影响逻辑,HR无法评估贡献真实性与难度。这在芯片设计中尤为关键,因为相同指标可能源于不同技术路径(如架构优化 vs. 工艺升级)。逻辑断裂易被怀疑成果夸大或团队功劳混淆,降低简历的可验证性。

- 采用‘行动-对象-结果-影响’结构,如‘通过优化时钟门控方案,使DDR子系统动态功耗降低20%,芯片待机时间延长15%’。

- 明确成果的技术驱动因素,如‘采用UPF多电压域设计,结合电源门控,实现待机功耗降低40%’。

- 关联成果与业务价值,如‘功耗优化使芯片通过客户严苛续航测试,助力产品中标某车企项目’。

角色定位模糊或夸大

使用‘负责’‘主导’等词汇描述项目角色,但未清晰界定个人贡献边界(如模块级 vs. 芯片级),HR易通过项目规模、团队构成、周期长度交叉验证发现矛盾。这在流片周期长、协作紧密的芯片行业尤为敏感,角色夸大可能直接导致简历被否决。

- 精确描述角色范围,如‘负责UART IP模块的RTL设计与验证’而非‘负责芯片通信子系统’。

- 在成果句中补充协作背景,如‘作为子系统设计负责人,协调3人团队完成DDR接口集成,时序收敛达标’。

- 使用量化证据支撑角色,如‘主导芯片级验证计划制定,覆盖2000+测试用例,提前2周完成签核’。

流程描述脱离行业实际

泛泛描述设计流程(如‘参与从RTL到GDSII’),但未体现行业特有环节(如MPW流片决策、硅后调试、Foundry对接)或挑战细节。这使简历缺乏行业辨识度,HR难以判断候选人是否具备真实项目经验,易被视为模板化表述而降低竞争力。

- 嵌入行业标准流程节点,如‘参与芯片MPW流片全过程,包括时序签核、DFT插入与封装联合仿真’。

- 突出流程中的难点解决,如‘处理7nm工艺下IR-drop分析,确保电源完整性达标通过DRC检查’。

- 使用行业通用时间标志,如‘项目周期18个月,包含2次MPW流片与1次量产验证’。

💡 检验每句表述:能否回答‘为什么这么做、结果是什么、影响了什么’,确保逻辑闭环与证据可追溯。

薪酬概览

平均月薪

¥44000

中位数 ¥0 | 区间 ¥33300 - ¥54600

近一年ASIC Design Engineer薪资整体呈上涨趋势,一线城市薪酬水平明显高于其他地区。

来自全网 12 份数据

月薪分布

91.7% 人群薪酬落在 >30k

四大影响薪酬的核心维度

影响薪资的核心维度1:工作年限

全国范围内,3-5年经验是薪资增长关键期,8年后增速放缓,经验价值趋于稳定。

影响因素

- 初级(0-2年):掌握基础设计流程,薪资随技能熟练度稳步提升。

- 中级(3-5年):独立负责模块设计,薪资因项目复杂度与责任增加而显著增长。

- 高阶(5-8年):主导项目或团队,薪资受技术深度与业务价值驱动。

- 资深(8-10年+):具备架构或管理能力,薪资增长依赖战略贡献与行业影响力。

💡 薪资增长并非线性,建议关注3-5年关键期,同时结合个人技术深度与项目成果综合评估。

影响薪资的核心维度2:学历背景

学历差距在入行初期明显,高学历溢价随经验增长逐渐收敛

影响因素

- 专科:侧重实践技能,薪资受岗位匹配度与行业经验影响较大

- 本科:具备系统专业知识,薪资随技术深度与项目经验稳步提升

- 硕士:强化研究与应用能力,薪资因技术复杂性与创新价值而增长

- 博士:专注前沿技术研发,薪资受学术成果与行业影响力驱动

💡 学历溢价在职业生涯初期较为明显,长期薪资增长更依赖实际能力与项目成果

影响薪资的核心维度3:所在行业

全国范围内,技术密集型行业薪资优势明显,行业景气度与人才稀缺度是主要驱动因素

| 行业梯队 | 代表行业 | 高薪原因 |

|---|---|---|

| 高价值型 | 半导体/集成电路 | 技术壁垒高,研发投入大,人才供需紧张,行业盈利能力较强 |

| 增长驱动型 | 人工智能/芯片设计 | 技术创新活跃,市场增长快,对高端人才需求旺盛,经验价值高 |

| 价值提升型 | 消费电子/通信设备 | 产业规模大,业务复杂度高,经验积累对薪资提升作用明显 |

影响因素

- 行业景气度直接影响薪资水平,高增长行业通常提供更高薪酬回报

- 技术密集度与人才稀缺度是决定行业薪资溢价的关键因素

- 行业经验价值随业务复杂度和技术深度提升而增加

💡 行业选择影响长期薪资成长潜力,建议结合个人技术专长与行业发展趋势综合考量

影响薪资的核心维度4:所在城市

一线城市薪资水平领先,新一线城市增长较快,二线城市薪资与生活成本更平衡

| 城市 | 职位数 | 平均月薪 | 城市平均月租 (两居室) | 谈职薪资竞争力指数 |

|---|---|---|---|---|

1成都市 | 7 | ¥47200 | ¥2500 | 80 |

2南京市 | 7 | ¥34600 | ¥3000 | 60 |

3西安市 | 6 | ¥30000 | ¥2000 | 10 |

4上海市 | 12 | ¥44000 | ¥6100 | 0 |

影响因素

- 行业集聚度直接影响薪资水平,产业集中区域通常提供更高薪酬回报

- 城市经济发展阶段决定岗位复杂度与薪资天花板,发达城市机会更多

- 人才流动与城市吸引力形成联动,人才流入多的城市薪资竞争力更强

- 生活成本与薪资购买力需综合考量,高薪资城市往往伴随更高生活支出

💡 城市选择需平衡薪资水平与生活成本,一线城市机会多但压力大,新一线城市成长性较好

市场需求

8月新增岗位

47

对比上月:岗位减少0

全国ASIC Design Engineer岗位需求近期保持稳定增长,招聘热度较高

数据由各大平台公开数据统计分析而来,仅供参考。

抱歉,岗位需求趋势暂无数据

不同经验岗位需求情况

全国ASIC Design Engineer岗位需求以中级经验为主,初级与高级岗位需求相对均衡,整体覆盖完整职业周期

| 工作年限 | 月度新增职位数 | 职位占比数 |

|---|---|---|

| 应届 | 3 | 7% |

| 1-3年 | 3 | 7% |

| 3-5年 | 19 | 44.2% |

| 5-10年 | 11 | 25.6% |

| 不限经验 | 7 | 16.3% |

市场解读

- 初级人才需求稳定,企业注重基础技能与培养潜力,入行门槛相对适中

- 中级经验岗位需求最为旺盛,企业看重独立项目经验与技术深度,即战力价值突出

- 高级人才需求集中在技术攻关与团队管理,市场稀缺性明显,战略价值较高

- 全国整体呈现中级经验主导、初级与高级补充的稳健需求结构

💡 建议根据自身经验阶段关注对应需求热点,中级经验求职者当前市场机会相对更多

不同行业的需求分析

全国ASIC Design Engineer需求集中在半导体、人工智能、消费电子等行业,技术密集型领域招聘活跃

市场解读

- 半导体行业需求旺盛,受国产化与技术创新驱动,对ASIC设计人才需求持续增长

- 人工智能领域招聘活跃,芯片设计在AI加速、边缘计算等场景的应用推动岗位扩张

- 消费电子行业需求稳健,产品迭代与性能提升需要ASIC设计支持,岗位机会稳定

- 通信设备与汽车电子等新兴领域需求逐步增加,行业多元化带来更多应用场景

💡 建议关注半导体与人工智能等增长行业,同时积累跨行业应用经验以提升职业适应性