Memory Compiler设计专家(J10160)

3-5万杭州市硕士不限经验

职位描述

1. 存储器编译器设计与开发 -主导或参与SRAM、ROM、Register File等存储单元编译器(Memory Compiler)的架构设计、电路优化及版图生成工具开发。确保设计符合的设计规则(DRC/LVS)、可靠性要求(如电迁移、噪声容限)及良率目标。

2. 工艺适配与性能优化 - 深入理解工艺特性(如寄生参数、器件匹配性、电压降效应),优化存储单元的面积、功耗、速度(时序收敛)PPA和稳定性(SNM/Write Margin)。 解决因短沟道效应、漏电问题导致的存储单元性能挑战。

3. 跨团队协作 - 与工艺团队(Foundry)对接,确保工艺参数准确集成至设计流程;支持客户或SoC团队完成存储器模块的定制化需求,提供时序模型(Liberty)、功耗模型及物理版图集成方案。

4. 自动化流程开发 - 开发脚本工具(Python/Tcl/Perl)优化编译器自动化流程,提升生成效率与可扩展性;构建验证框架,确保输出结果(GDSII、网表、时序模型)的准确性。

5. 技术文档与问题支持- 编写设计指南、用户手册及问题排查文档;协助解决客户在流片或测试阶段遇到的存储单元相关问题。

任职资格:

1.15年以上存储器编译器或定制电路设计经验,至少参与过2个先进工艺的流片项目。

2.有低功耗、高速高密度Memory compiler设计经验,

3.熟悉Memory Compiler生成流程, 具备Python/Tcl/Perl脚本开发经验。

4.掌握存储单元电路设计(如6T-SRAM、Dual-Port Memory)及时序/功耗优化方法。

5.熟悉PDK中的器件模型、设计规则及可靠性约束。

6.熟练使用 Virtuoso、PrimeSim XA、Calibre等工具完成电路仿真、版图设计及物理验证。

7.微电子学、集成电路设计、电子工程等相关专业硕士或博士学历。

8.具备较强的逻辑分析能力与抗压能力,能独立解决复杂技术问题。

9.良好的团队协作意识,适应多任务并行工作模式。

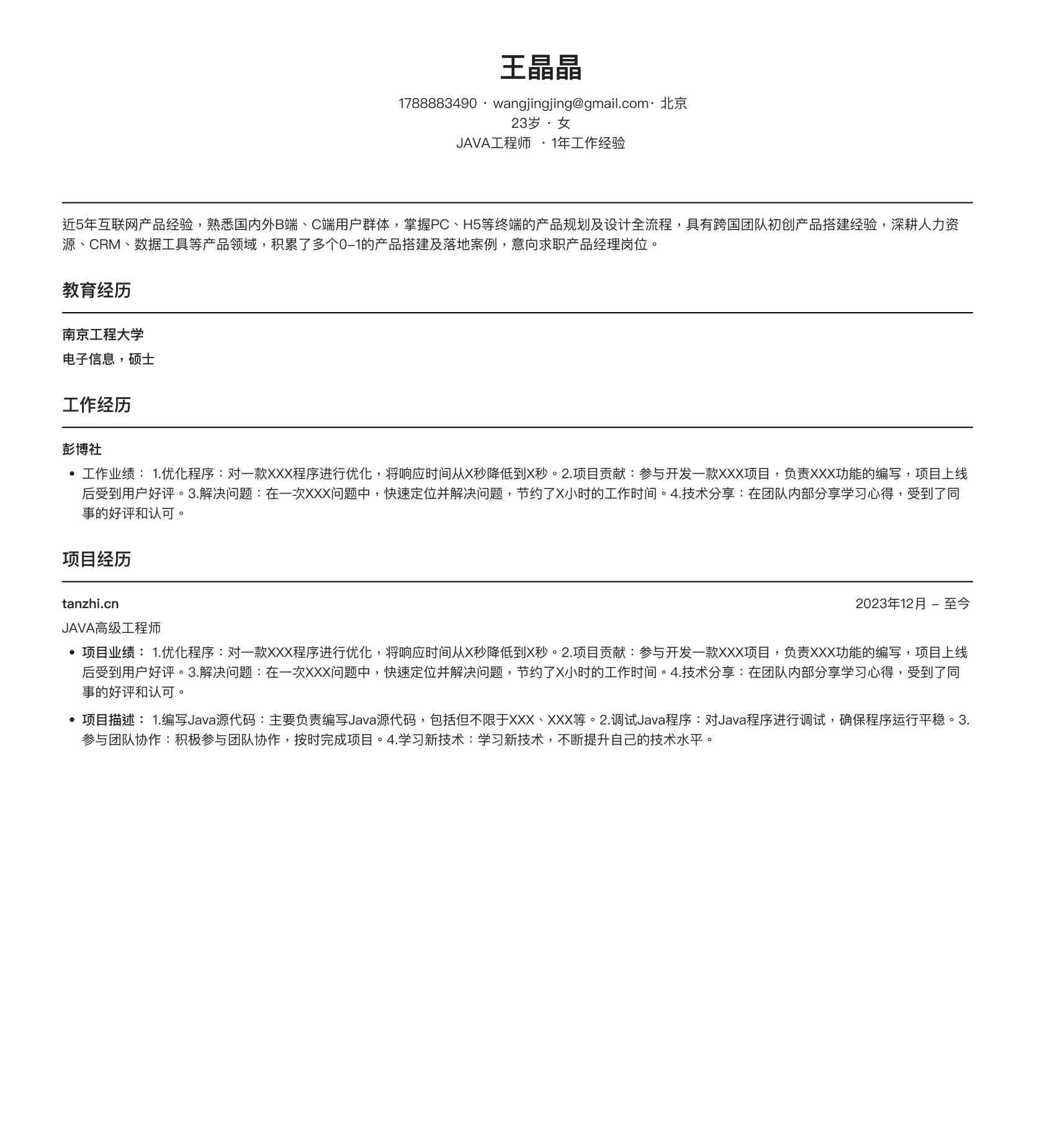

简历是否与目标岗位匹配?

为什么没有面试?我的简历有什么问题?

怎么优化?职业优势在哪里?

投递之前...

你的简历真的准备好了吗

80% 简历因职业定位模糊,表达无焦点

被快速跳过,立即诊断,提升面试机会!